Used to evaluate damage caused by charge-up of 300mm and 200mm devices that perform plasma processing.We also provide chip services and can evaluate devices with non-standard board sizes.

Charge-Up Monitor Wafers

Charge-Up Monitor Wafers

1. 300mm Charge Up Monitor Wafer (Mask: PT013)

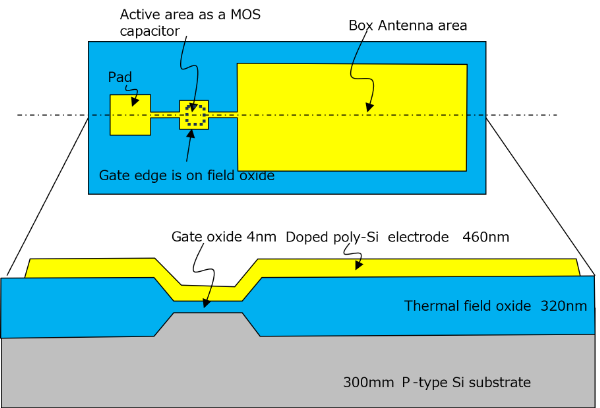

TEG structure

Element isolation is performed using LOCOS, and a MOS capacitor is formed using a phosphorus-doped Poly Si electrode and a 4nm thermal oxide film.The degree of charge-up is evaluated using antennas with different areas attached to the Poly Si electrode.

Electrical Measurements after Plasma Treatment

The breakdown voltage of the gate insulating film (4nm thermal oxide film) is measured by I-V measurement after plasma processing of the wafer.

By mapping the breakdown voltage on the wafer for each antenna ratio and color-coding it according to the breakdown voltage, it is possible to identify the wafer area where charge-up is likely to occur and the degree of damage. Typically, approximately 25% of the effective chips are measured in a checkerboard pattern.

We sell wafers including measurement services.

2. 200mm Charge Up Monitor Wafer

The TEG used for charge-up monitors uses the same pattern for 300mm and 200mm.

The gate insulating film is a 4nm thermal oxide film, which is the same, but the thickness of the Poly Si electrode is 150nm, which is thinner than his 300nm and 300mm wafers, so please contact us regarding the purpose of use.

Normal measurement measures the inner half of the effective chip.

3. Charge Up Monitor Chips

The process of retrieving chips

After dicing charge-up monitor wafers, we sell them in sets of 4 in a case.

Measurements will be performed in units of 4.Please contact us for details on how to use.